Research Summary

The increasing complexity of applications requires faster processing with effective utilization of computing resources. Modern systems often handle a large amount of data and need to provide real-time performance in many applications. Such systems need to be deployed on various kinds of platforms from wireless embedded devides to high-end workstations. Our development mainly concentrate on GPP based embedded system solutions achieving high degree of programmability to GPU/Multi-core CPU based high-performance computing.

Main focus of research work is towards designing:

- Edge AI

- Edge Computing

- Application Specific Processor Design

- VLSI architecture for real-time signal/image processing/AI/ML

- Energy-efficient Computing

- High performance embedded computing

Research Interests

-

Hardware implementation of CNN for Object Tracking, License Plate Recognition

FPGA/Microcontroller based implementation of Convolution Neural Network (CNN)

-

Hardware architecture for Visual Object Tracking, Face Detection, Face recognition, Intelligent transport systems

Deep learning based implementation

-

Architecture optimization for low-power IoT applications

-

Hardware implementation of Packet classifier using Net-FPGA

-

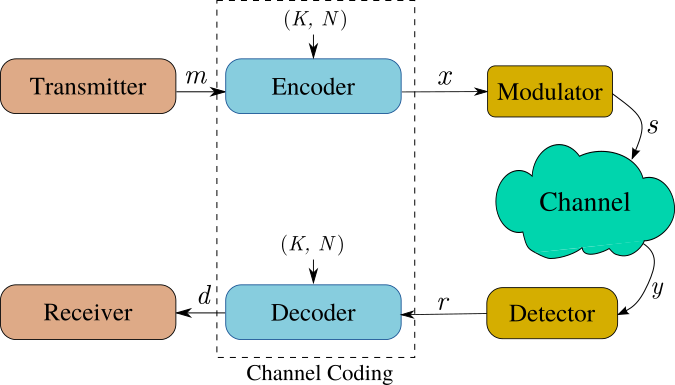

Current research on LDPC decoders focuses on efficient code design, throughput, and hardware reconfigurability. Most research work has focused on a new class of hardware efficient codes called quasi-cycle (QC) LDPC code, which have efficient architecture for decoding. We adress the architecture challenges of QC-LDPC decoder with short length and variable rate LDPC code.

Research Projects (Ongoing)

Research Projects (Completed)

-

Hardware design for channel decoder using low-density parity-check (LDPC) codes: Current research on LDPC decoders focuses on efficient code design, throughput, and hardware reconfigurability. Most research work has focused on a new class of hardware efficient codes called quasi-cycle (QC) LDPC code, which have efficient architecture for decoding. We adress the architecture challenges of QC-LDPC decoder with short length and variable rate LDPC code.

Laboratory Personel

These students and staff members are associated with Embedded System Laboratory.